FPGA完全入门教程

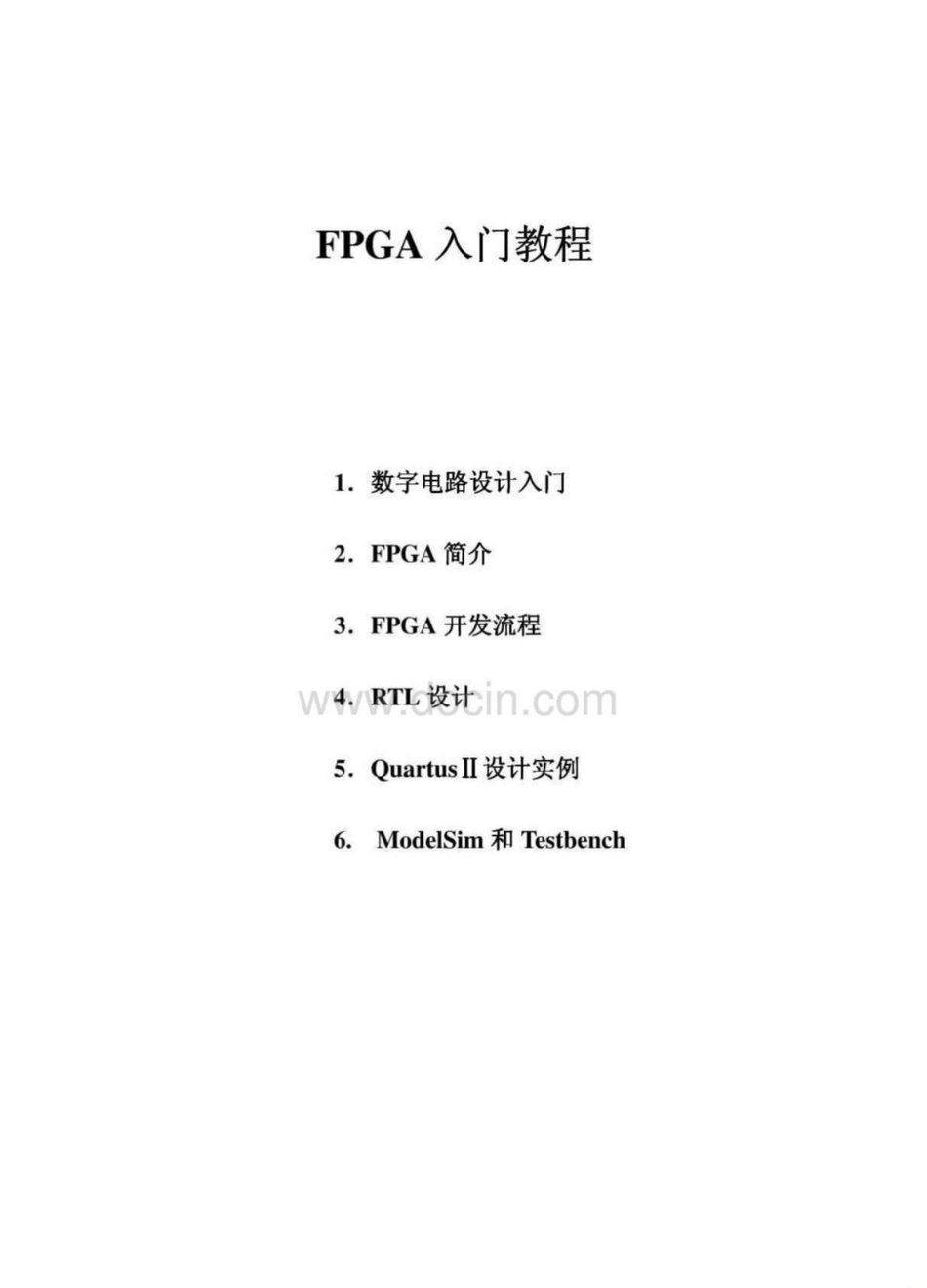

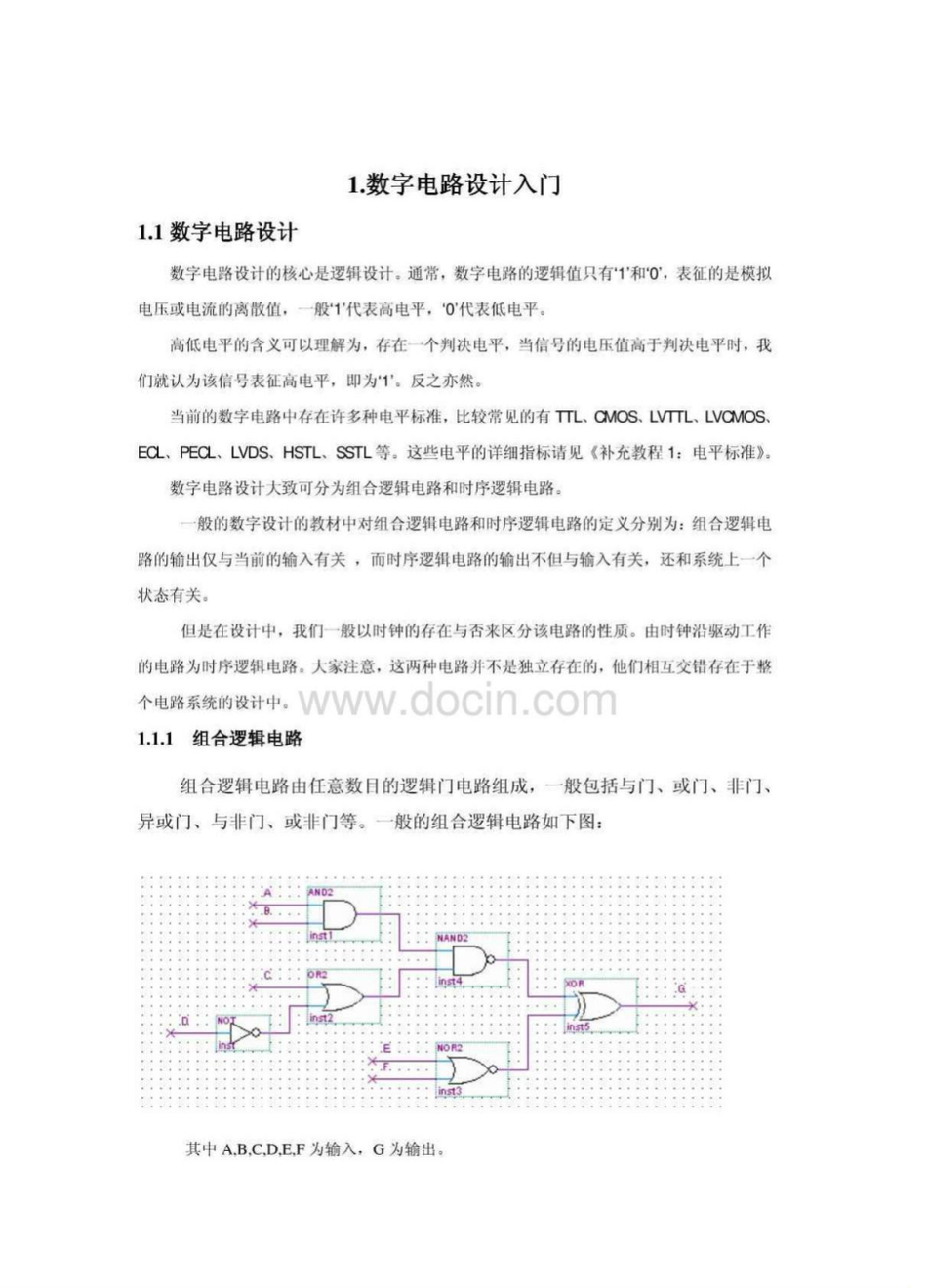

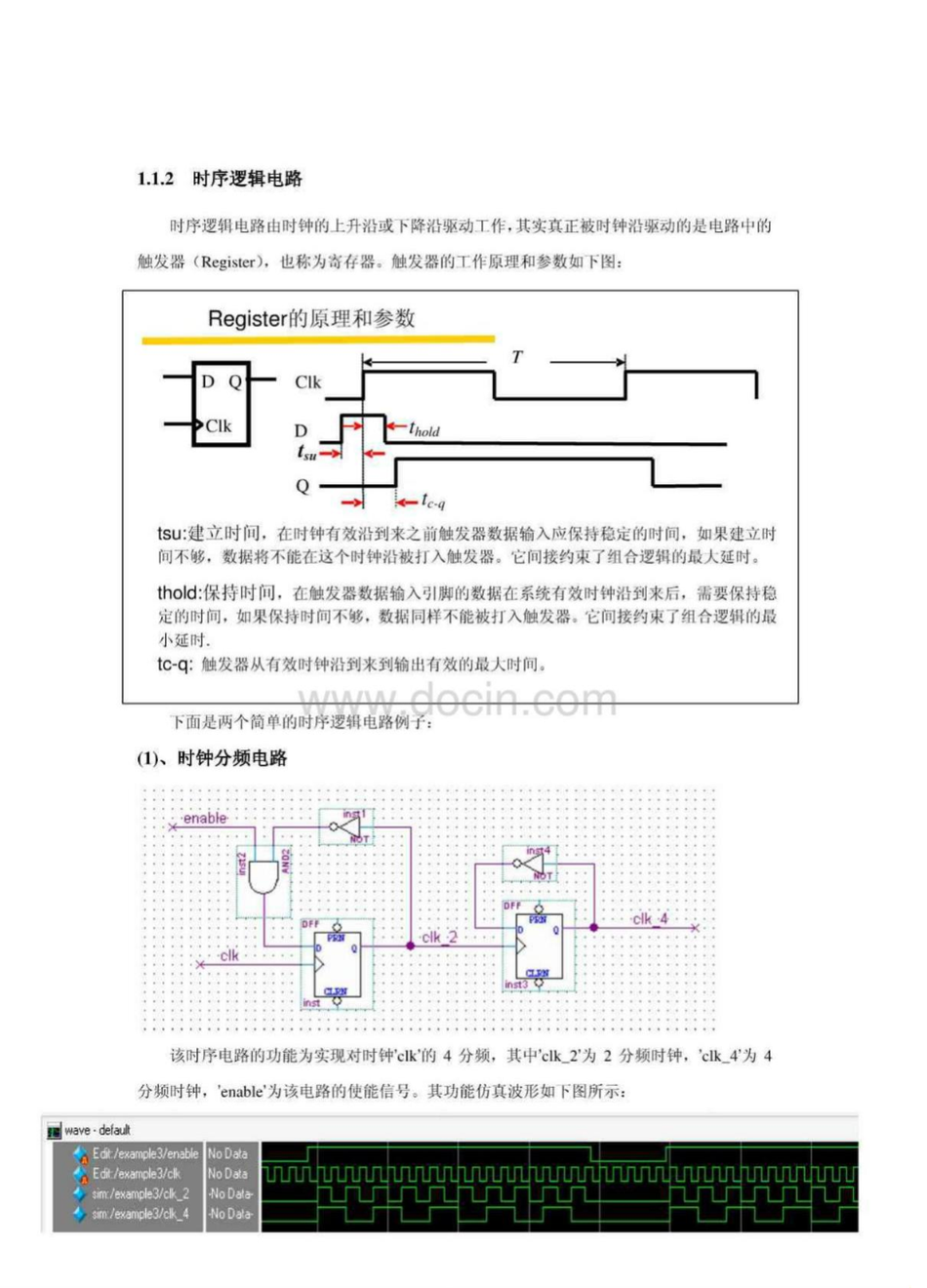

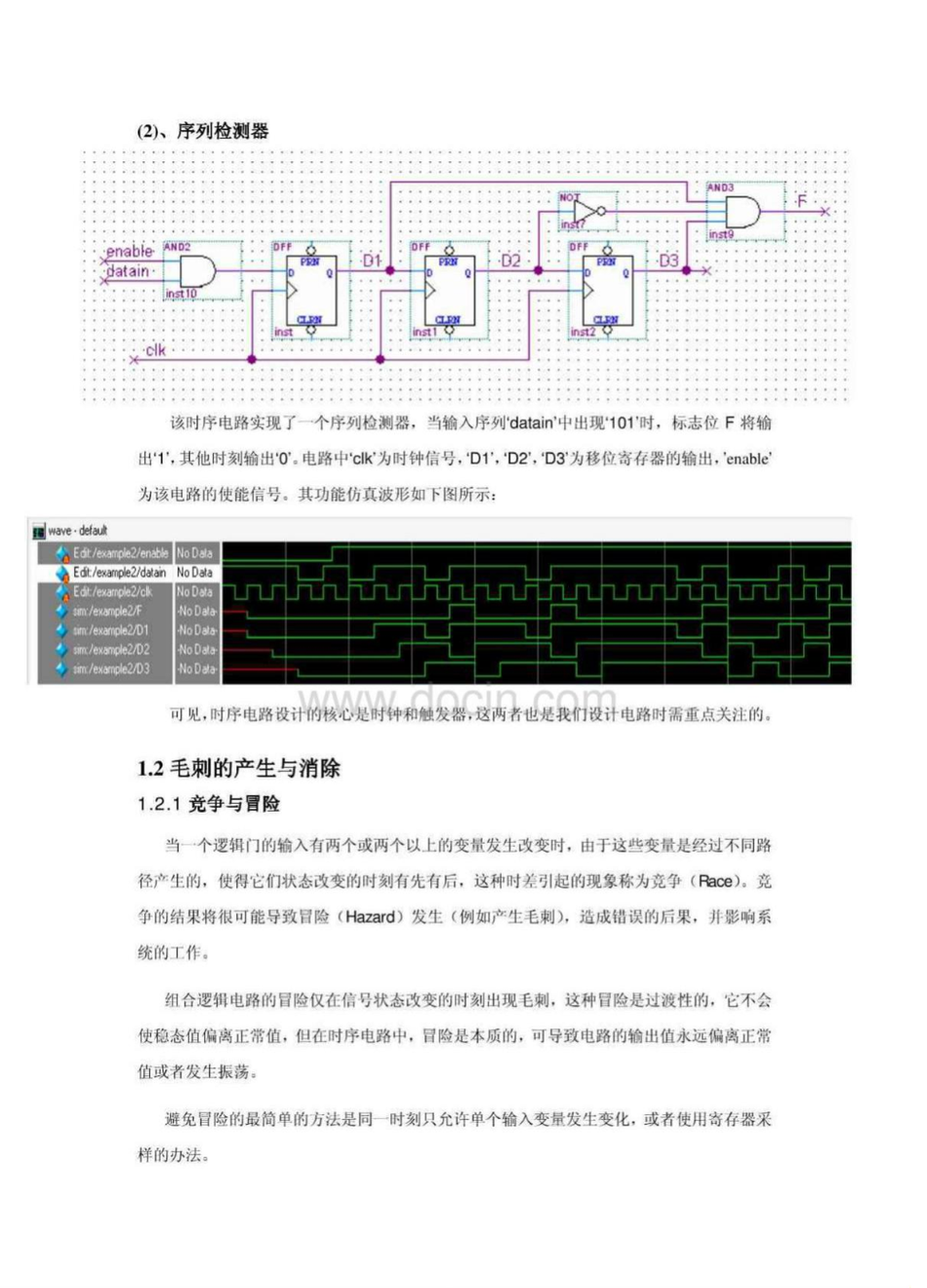

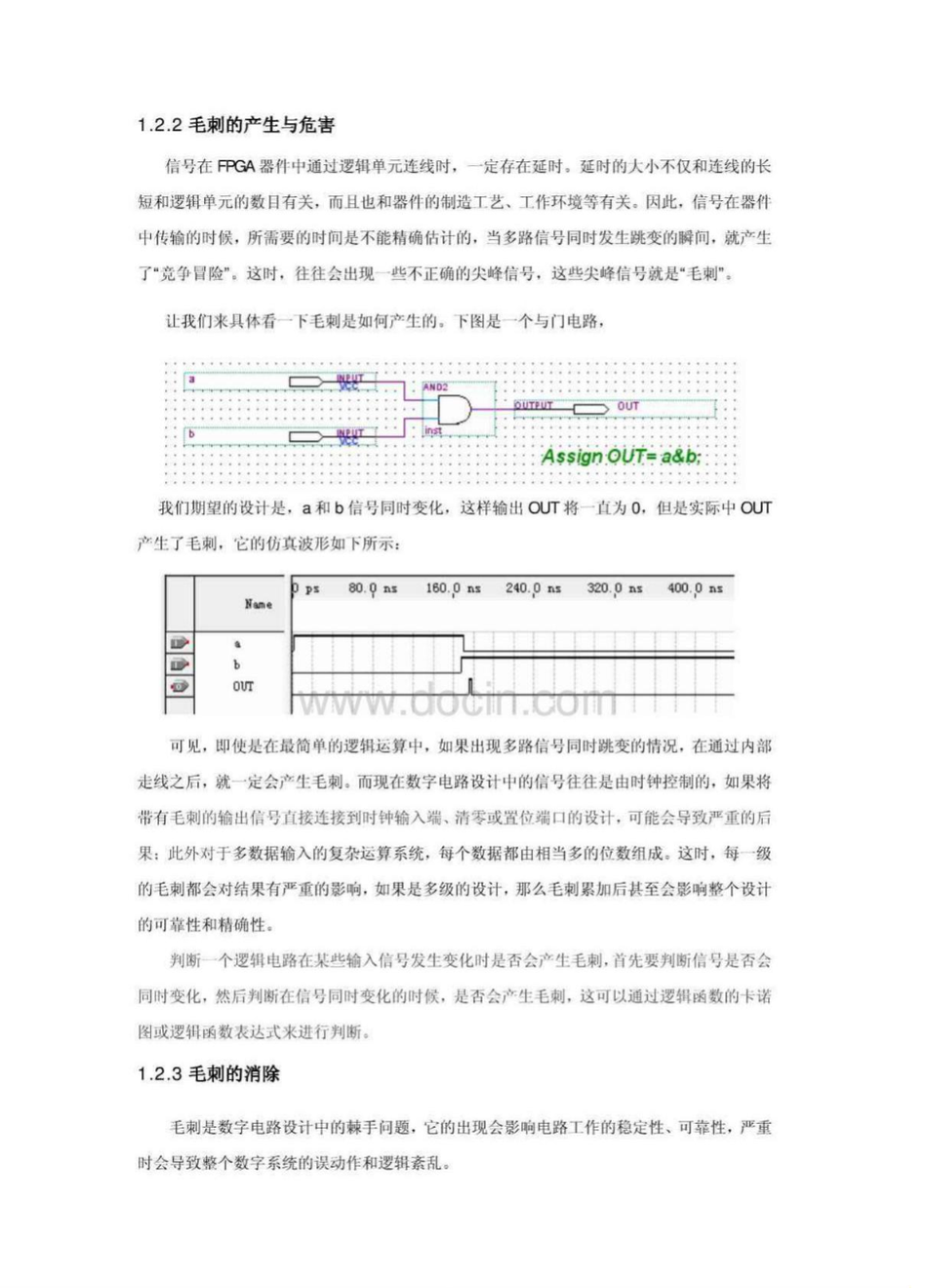

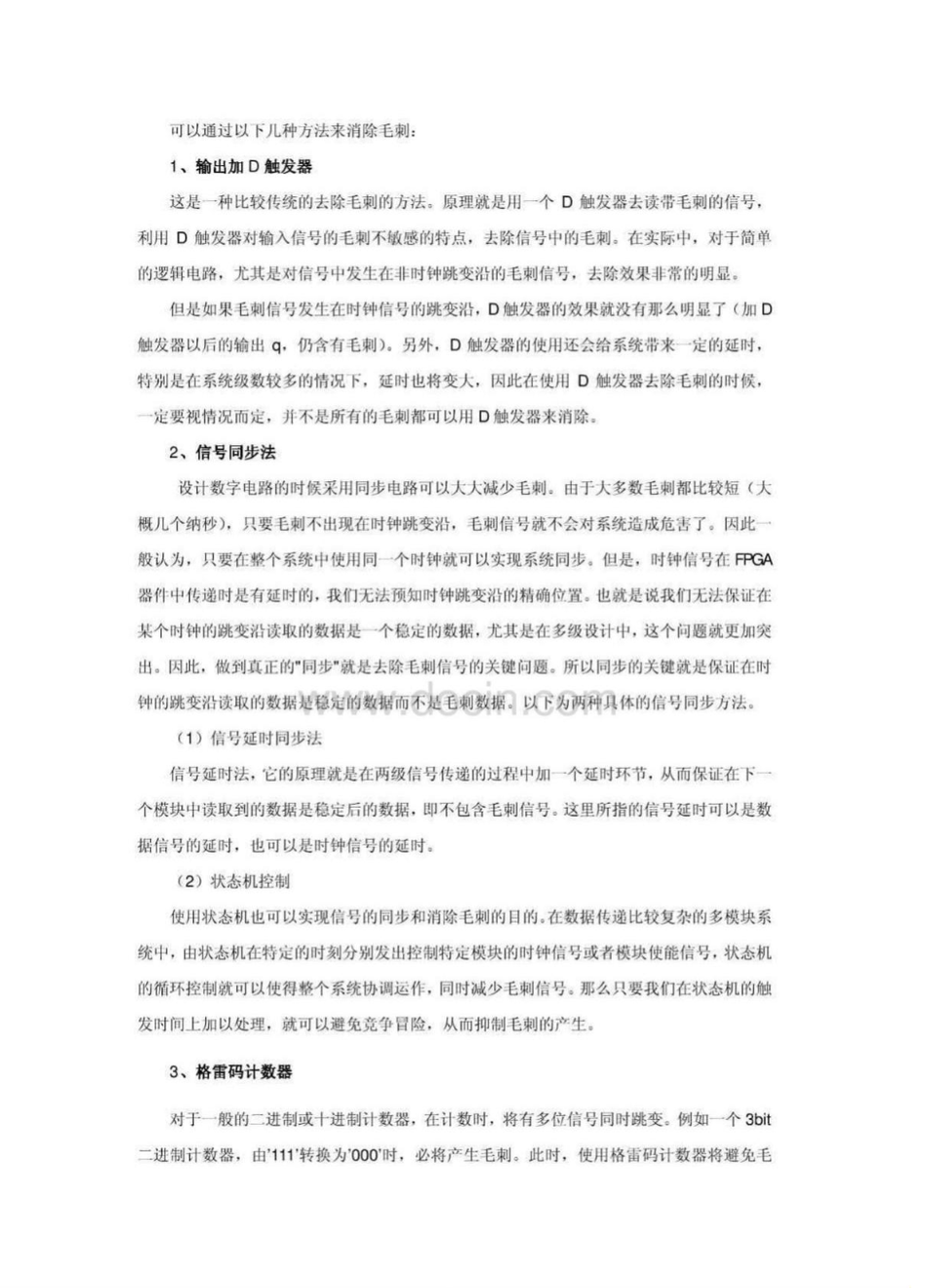

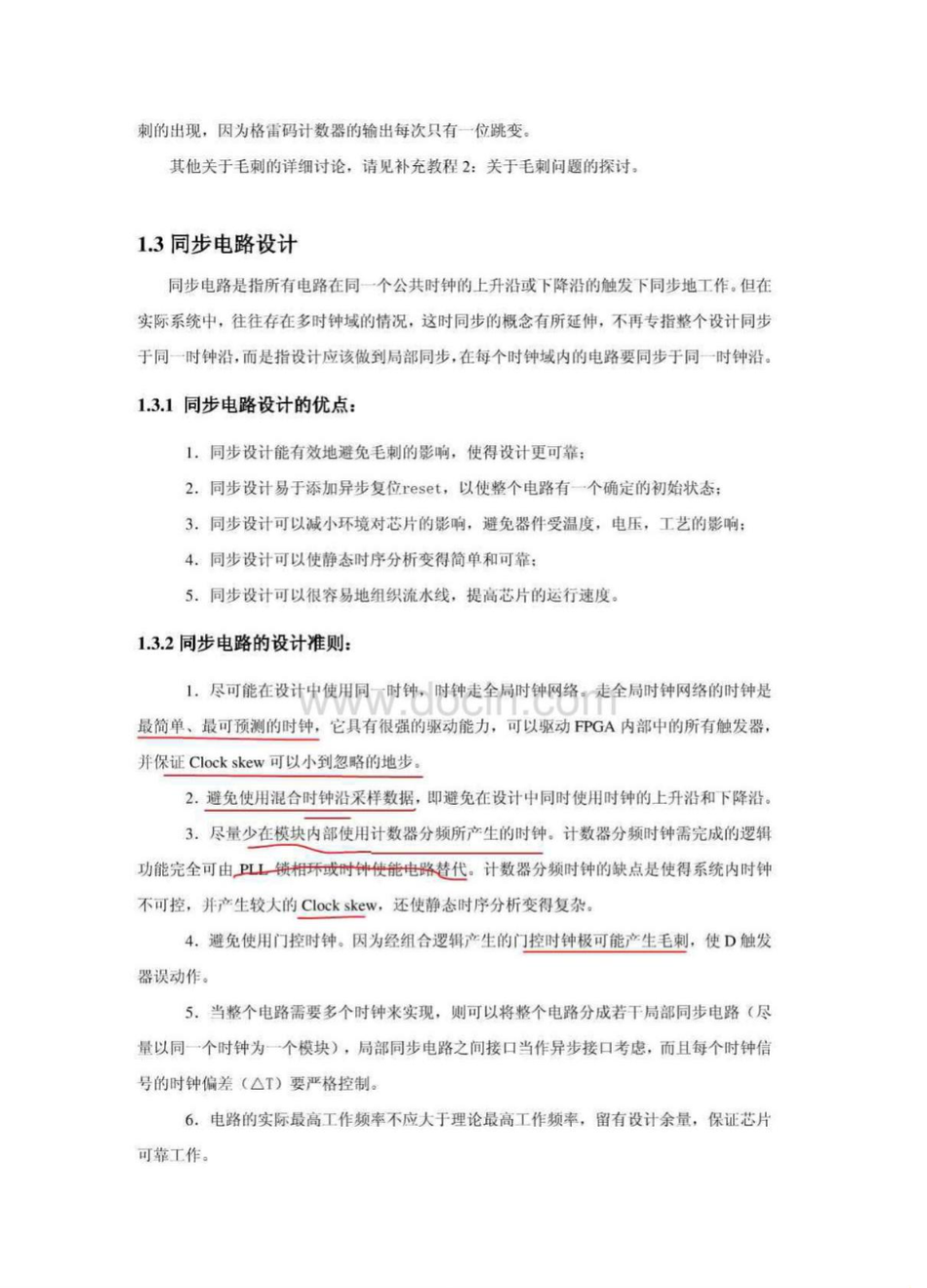

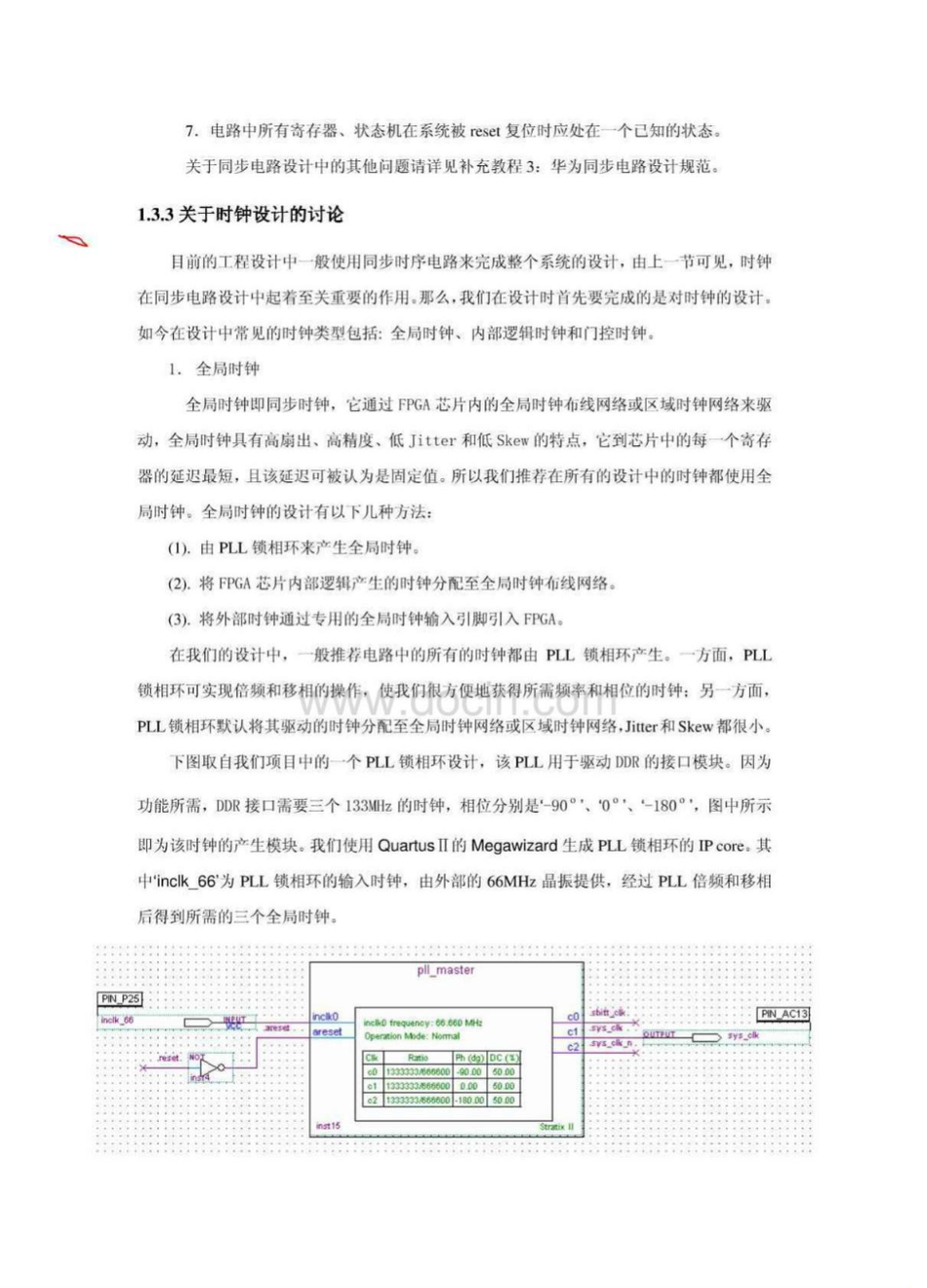

FPGA开发技术教程 FPGA完全入门1.12时序逻辑电路时序逻辑电路由时钟的上升沿或下降沿驱动工作,其实真正被时钟沿驱动的是电路中的触发器( Register),也称为寄存器。触发器的工作原理和参数如下图Register的原理和参数QClk- Clkholdtsu:建立时间,在时钟有效沿到来之前触发器数据输入应保持稳定的时间,如果建立时间不够,数据将不能在这个时钟沿被打入触发器。它间接约束了组合逻辑的最大延时。thold:侏持时间,在触发器数据输入引脚的欻据在系统有效时钟沿到来后,需要保持稳定的吋间,如果保持吋间不够,数据同样不能被打入触发器。它间接约束了组合逻辑的最小延时tcq:触发器从有效时钟沿到来到输出有效的最大时间。下面是两个简单的时序逻辑电路例子:(1)、时钟分频电路enate:-···TT靠:11:DFFc‖k4lk.2∴∴;;;;:咳时序电路的功能为实现对时钟"clk'的4分频,其中'clk2为2分频时钟,'lIk4'为4分频时钟,' enable'为该电路的使能信号。其功能仿真汲形如卜图所示:wave. defaultEdt /example /enable No DataE dt es神3体 as uuuyuuuuyuuuuuyuuuyuuLuLuyuuunsim/exampe3/ck-2 Dalasim:/exampe3/ck_4 No Data(2)、序列检测器EAND3FInenable. AND2DFFB2datain::,:intinst1 Q)使该时序电路实现了一个序列检测器,当输入序列 datain中出现‘101时,标志位F将输出1,其他时刻输出0:电路中ck'为时钟信号,D1,D2,D3’为移位寄存器的输出,' enable为该电路的使能信号。其功能仿真波形如下图所示:遥wse:asim/example2/FNo Dalan /example21小 oDalasin:/example2/D2 No Dalasm/exaple 2/D3 I-No Data:可见,时序电路设计的核心是时钟和触发备,这两者也是我们设计电路时需重点关注的。12毛刺的产生与消除1.2.1竞争与冒险当一个逻辑门的输入有两个或两个以上的变量发生改变时,由于这些变量是经过不同路径产生的,使得它们状态改变的时刻有先有后,这种时差引起的现象称为竞争(Race)。竟争的结果将很可能导致冒险( Hazard)发生(例如产生毛刺),造成错误的后果,并影响系统的工作。组合逻辑电路的冒险仅在信号状态改变的时刻出现毛刺,这种冒险是过渡性的,它不会仗稳态值偏离正常值,但在时序电路中,冒险是本质的,可导致电路的输出值永远偏离正常值或者发生振荡避免冒险的最简单的方法是同一时刻只允许单个输入变量发生变化,或者使用寄存器采样的办法。122毛刺的产生与危害信号在FA器件中通过逻辑单元连线时,一定存在延时。延时的大小不仅和连线的长短和逻弭单元的数目有关,而且也和器件的制造工艺、工作环境等有关。因此,信号在器件屮传输的时候,所需要的时间是不能精确估计的,当多路信号同时发生跳变的瞬间,就产生了“竞争冒险”。这时,往往会出现一些不正确的尖峰信号,这些尖峰信号就是“毛刺让我们来具体看一下毛刺是如何产生的。下图是一个与门电路,c,,典NDQUT+喜4Assign OUT= a&b;(+++“++-+++++-++--+4-+--+-+--+“““我们期望的设计是,a和b信号同时变化,这样输出OUT将一直为0,但是实际中OUT产生了毛刺,它的仿真波形如下所示P80.a1600n240.9n320.0as400,0nsbQUT可见,即使是在最简单的逻辑运算中,如果出現多路信号同时跳变的情况,在通过内部走线之后,就一定会产生毛刺。而现在数字电路设计中的信号往往是由时钟控制的,如果将带有毛東的输出信号直接连接到时钟输入端、清零或置位端口的设计,可能会导致严重的后果:此外对于多数据输入的复杂运算系统,每个数据都由相当多的位数组成。这时,每一级的毛刺都会对结果有严重的影响,如果是多级的设计,那么毛刺累加后甚至会影响整个设计的可靠性和精确性。判断一个逻辑电路在某些输入信号发生变化时是否会产生毛刺,首先要判断信号是否会同时变化,然后判断在信号同时变化的时侯,是否会产生毛刺,这可以通过逻辑函数的卡诺图或逻辑函数表达式来进行判断。1.23毛刺的消除毛刺是数字电路设计中的棘于问题,它的出现会影响电路工作的稳定性、可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。可以通过以卜儿种方法来消除毛刺1、输出加D触发器这是一种比较传统的去除毛刺的方法。原理就是用一个D触发器去读带毛刺的信号,利用D触发器对输入信号的毛刺不敏感的特点,去除信号中的毛刺。在实际中,对于简单的逻辑电路,尤其是对信号中发生在非时钟跳变沿的毛刺信号,去除效果非常的明显但是如果毛刺信号发生在时钟信号的跳变沿,D触发器的效果就没有那么明显了(加D触发器以后的输出q,仍含有毛刺)。另外,D触发器的使用还会给系统带来一定的延时,特别是在系统级数较多的情况下,延时也将变大,因此在使用D触发器去除毛刺的时候一定要视情况而定,并不是所有的毛刺都可以用D触发器来消除。2、信号同步法设计数字电路的时候采用同步电路可以大大减少毛刺。由于大多数毛刺都比较短(大概几个纳秒),只要毛刺不出现在时钟跳变沿,毛刺信号就不会对系统造成危害了。因此一般认为,只要在整个系统中使用同一个时钟就可以实现系统同步。但是,时钟信号在FGA器件中传递时是有延时的,我们无法预知时钟变沿的精硫位置。也就是说我们无法保证在某个时钟的跳变沿读取的数据是一个稳定的数据,尤其是在多级设计中,这个问题就更加突出。因此,做到真正的"同步”就是去除毛刺信号的关键问题。所以同步的关键就是保证在时钟的跳变沿读取的数据是稳定的数据而不是毛刺数据。以下为两种具体的信号同步方法。(1)信号延时同步法信号延时法,它的原理就是在两级信号传递的过程中加一个延时环节,从而保证在下一个模块巾读取到的数据是稳定后的数据,即不包含毛刺信号。这里所指的信号延时可以是数据信号的延时,也可以是时钟信号的延时。(2)状态机控制使用状态机也可以实现信号的同步和消除毛刺的目的。在数据传递比较复杂的多模块系统中,庄状态机在特定的时刻分别发出控制岢定模垬的吋钟信号或者模块使能信号,状态机的循环控制就可以使得整个系统协调运作,同吋减少毛刺信号。那么只要我们在状态机的触发吋间上加以处理,就可以避兔竞争冒险,从而抑制毛刺的产生。3、格雷码计数器对于一般的二进制或十进制计数器,在计数时,将有多位信号同时跳变。例如一个3bit二进制计数器,由11'转换为000时,必将产生毛刺。此时,使用格雷码计数器将避免毛刺的出现,因为格雷码计数器的输出每次只有一位跳变。其佃关于毛刺的详细讨论,请见补充教程2:关于毛刺问题的探讨。13同步电路设计同步电路是指所有电路在同一个公共时钟的上升沿或下降沿的触发下同步地工作。但在实阪系统中,往往存在多时钟域的情况,这时同步的概念有所延伸,不再专指整个设计同步于同一时钾沿,而是指设计应该做到局部同步,在每个时钟域内的电路要同步于同一时钟沿。131同步电路设计的优点:1.同步设计能有效地避免毛刺的影响,使得设计更可靠;2.同步设计易于添加异步复位 reset,以使璺个电路有个确定的初始状态;3.同步设计可以減小环境对芯片的影响,避免器件受温度,电压,工艺的影响4.同步设计可以使静态时序分析变待简单和可靠;5.同步设计可以很容易地组织流水线,提高芯片的运行速度。132同步电路的设计准则:1.尽可能在设计史使用同时钟时钟走全局时钟网终走全局时钟网络的时钟是最简单、最可预测的时钟,它具有很强的驱动能力,可以驱动FFGA内部中的所有触发器,并保证 Clock skew可以小到忽略的地步2.避免使用混合时钟沿采样数据,即避免在设计中同时使用时钟的上升沿和下降沿。3.尽量少在模块内部使用计数器分颊所产生的时钟。计数器分频时钟需完成的逻辑功能完全可由PL锁柑坏或时钟使能电峰替代。计数器分频时钟的缺点是使得系统内时钟不可控,并产生较大的 Clock skew,还使静态时序分析变得复杂4.避免使用门控时钟。因为经组合逻辑产生的门控时钟极可能产生毛刺,使D触发器误动作。5.当整个电路需要多个时钟来实现,则可以将整个电路分成若于局部同步电路(尽量以同一个时钟为一个模块),局部同步电路之间接口当作异步接口考虑,而且每个时钟信号的时钭偏差(△T)要严格控制。6.电路的实际最高T作频率不应大于理论最高T作频率,留有设计余量,保证芯片可靠工作。7.电路中所有寄存器、状态机在系统被 reset复位时应处在一个已知的状态。关于同步电路设计中的其他问题请详见补夼教程3:华为冋步电路设计规范。133关于时钟设计的讨论日前的工程设计中一般使用同步时序电路来完成整个系统的设计,由上一节可见,时钟在同步电路设计中起着至关重要的作用那么,我们在设计时首先要完成的是对时钟的设计。如今在设计中常见的时钟类型包括:全局时钟、内部逻辑时钟和门控吋钟。1.全局时钟全局时钟即同步时钟,它通过FPGA芯片内的全局时钟布线网络或区域时钟网络来驱动,全局时钟具冇髙扇出、高精度、低 Jitter和低Skew的特点,它到芯片中的每一个寄存器的延迟最短,且该延迟可被认为是固定值。所以我们推荐在所有的设计中的时钟都使用全局时钟。全局时钟的设计有以下几种方法(1).由PLL镯相环来产生全局时钟。(2).将FPGA芯片内部逻辑产生的时钟分配至全局时钟布线网络。(3).将外部时钟通过专用的全局时钟输入引脚引入FPGA在我们的设计中,一般推荐电路中的所有的时钟都白PLL锁相环产生。一方面,PL锁相环可实现倍频和移相的操作,使我们很方便地藜得所需频率和相位的时钟:另一方面,PLL锁相环默认将其驱动的时钟分配至全局时钟网络或区域时钟网络, Jitter和Skew都很小下图取自我们项目中的一个PL锁相环设计,该PL用于驱动DR的接口模块。因为功能所需,DDR接口需要三个133NHz的时钟,相位分别是-90°、°、←180°,图中所示即为该时钟的产生模块。我们使用 QuartusⅡ Megawizard生成PLL锁相环的 IP core。其屮inck66为PLL锁相环的输入时钟,由外部的66MIz晶振提供,经过PL倍频和移相后得到所需的三个全局时钟pll_master++::::::::::PIN_ P25inelt,:∵:[NAC13面5··etnck0 frequenoy:6660M增c1ciksvaCOperation Mode: Normalsy: elkc21vsc,创R式[PdDc(36080050:E6m152.内部逻辑时钟内部逻辑时钟即指由芯片内部的缃合逻辑或计数器分频产生的时钟。对于组合逻缉时钟,特别是由多级组合逻辑产生的时钟,是要被严格禁止使用的,因为一方而组合逻辑极容易产生毛刺,特别是对多级组合逻辑:另一方面组合逻辑电路的Jtr和Skew比较大,这将恶化时钟的质量。所以,一般组合逻辑产生的内部时钟仅仅适用于时钟频率较低、时钟精度要求不高的情况。对于计数器分频产生的时钟,也应该尽量少地使用,因为这种时钟会带来比较大的延迟,降低设计的可靠性,也使得静态时序分析变得复杂。计数器分频时钟需完成的逻辑功能完全可由PLL锁相环或时钟使能电路替代还有一种由触发器产生的时钟一行波时钟,即一个触发器的输出用作另一个触发器的时钟输入。文中1.1.2节描述的时钟分频电路就是种行波时钟。因为各触发器的时钟之间产生较大的时间偏移,很容易就会违反建立时间、保捋时间的要求,导致亚稳态的发生。所以,这种行波时钟要被严格禁止使用。3.门控时钟一般情况下,应该避免使用门控时钟。因为经组合逻辑产生的门控时钟极可能产生毛刺,对系统造成很大危害。但对于某些功耗很大的系统而言,需要使用门控时钟来降低功耗。我们推荐使用右图中描述的门控时钟的设source clkm计,该设计一般不会产生毛刺和亚稳态的问题。gated_clk因为触发器免了毛刺的产生,而亚稳态具可能出现在源时钟的下降沿,但是随后它与源时钟低相位相与,最后不会产生影响。source clkclk engoutgated clk门控时钟最好只在顶层模块中出现,并将其分离到一个在顶层的独立模块中。这同时保证了底层的每个模块有单一的时钟,且在本模块卬的时钟不进行门控在补充教程4和补充教程5中,我们对时钟和时序的设计进行了更详细的讨论。134亚稳态在同步电路或异步电路中,如果触发器的 setup时间或hold吋间不能得到满足,就可能产生亚稳态,此时触发器输出端Q在有效吋钟沿之后比较长的一段吋间处于不确定的状态,在这段时间里Q端将会产生毛刺并不断振荡、最终固定在某一电压值上,此电压值并不一定等于原来数据输入端Dng npo的值。这段时间称为决断时间sLynenroneato bclk( resolution time)。经过决断时间之后,Q端将稳定到0或1上,但是究竞是0还是1,Samples adat这是随机的,与输入没有必然halkand meI E的关系。就物荐cac哈dsn亚稳态的危害主要体现在破坏系统得稳定性上,由于输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态除了导致逻辑误判之外,严重情况下输出0~1之间的中间电压值还会使下一级产生亚稔态(即导致亚稳态的传播)。逻辑误判将导致功能性错误,而亚稳态的传播则扩大丁故障面,严重时将导致系统崩溃在异步时序电路中更容易发生亚稳态,因为异步电路般具有多个时钟域,数据在两个吋钟域间传递时,非常容易导致 setup时间或hod时间不满足而发生亚稳态。在同步时序电路中,当两个触发器间的组合逻辑延迟过大时,会导致 setup时间不满足而发生亚稳态1-3.5对跨时钟域数据的处理对跨时钟域数据的处理的核心就是要保证下级吋钟对上级数据采样的 setup时间或hold时间满足要求,即尽量避免亚稳态的发生和传播。但是,我们知道,只要系统中有异步元件,亚稳态就是无法避免的,因此设计的电路首先要减少亚稳态导致错误的发生,其次要仅系统对产生的错误不敏感。我们推荐使用以下方法来解决异步时钟域数据同步问题。1.用触发器打两拍如下图,左边为异步输入端,经过两级触发器同步,在右边的输出将是同步的,而且该输出基本不存在亚稳态。其原理是即使第一个触发器的输出端存在亚稳态,经过一个CLK片期后,第二个触发器D端的电平仍未稳定的概率非常小,因此第二个触发器Q端基本不会产生亚稳态。然而,亚稳态是无法被根除的,一旦亚稳态发生,后果的严重程度依赖于你

用户评论