PLL的电源管理设计

锁相环(PLL)是现代通信系统的基本构建模块。PLL通常用在无线电接收机或发射机中,主要提供“本振”(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数或数模转换的时钟源。

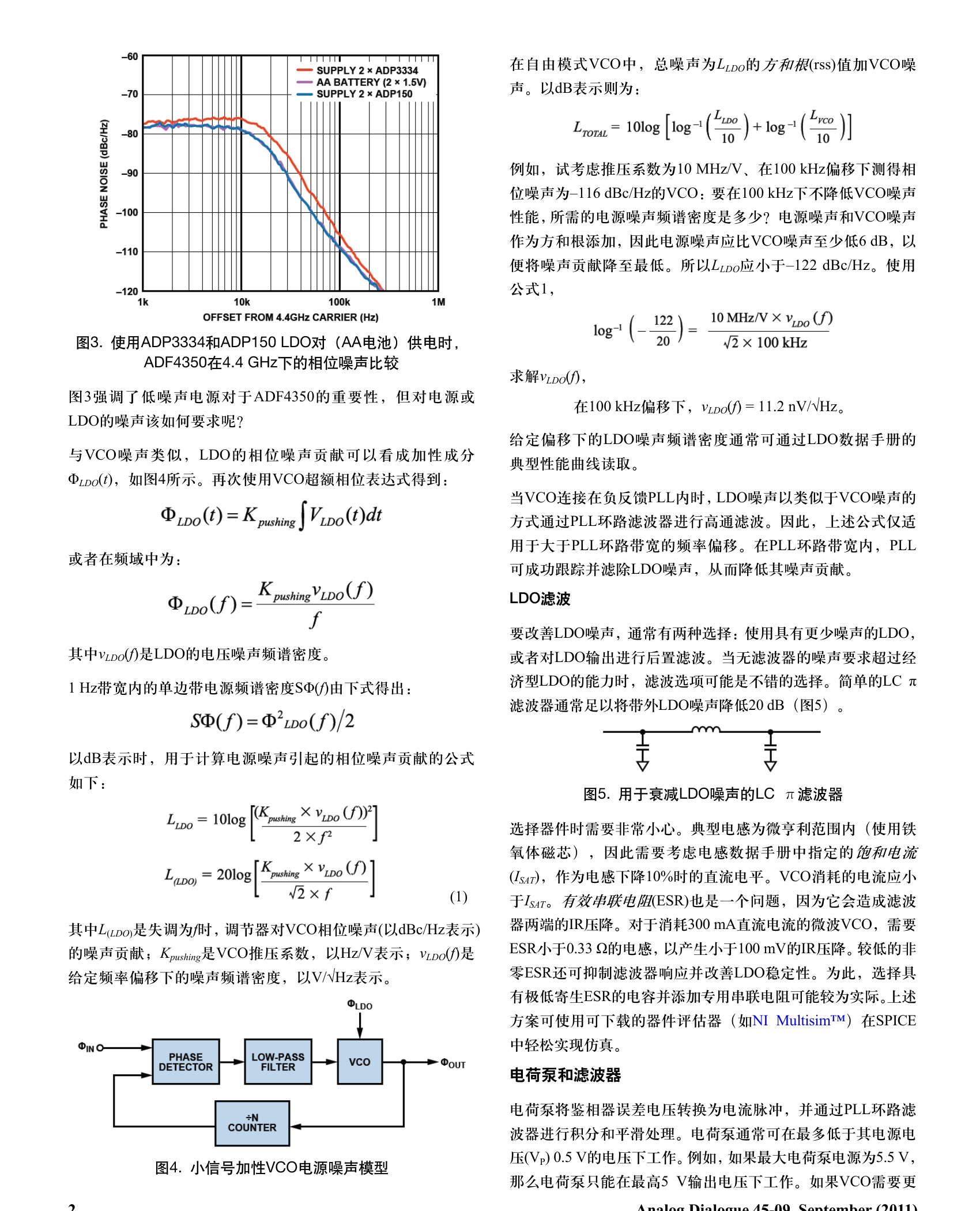

由于每一代PLL的噪声性能都在改善,因此电源噪声的影响变得越来越明显,某些情况下甚至可限制噪声性能。VCO推压的测量方法如下:向VTUNE引脚施加直流调谐电压,PLL的电源管理设计改变电源电压并测量频率变化。推压系数是频率变化与电压变化之比,如表1所示,使用的是ADF4350PLL。作者:^ìíá=e~êó和dêòêò=t~êò~表1.ADF4350VCO推压测量摘要VCOVtuneVVCO=3V时的VVCO=3.3V时的Kpushing=频段(V)f1(MHz)f2(MHz)Δf/ΔV锁相环(PLL)是现代通信系统的基本构建模块。PLL通常用在无(MHz/V)(MHz)线电接收机或发射机中,主要提供“本振”(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数或22002.522

用户评论