Verilog代码书写规范Release

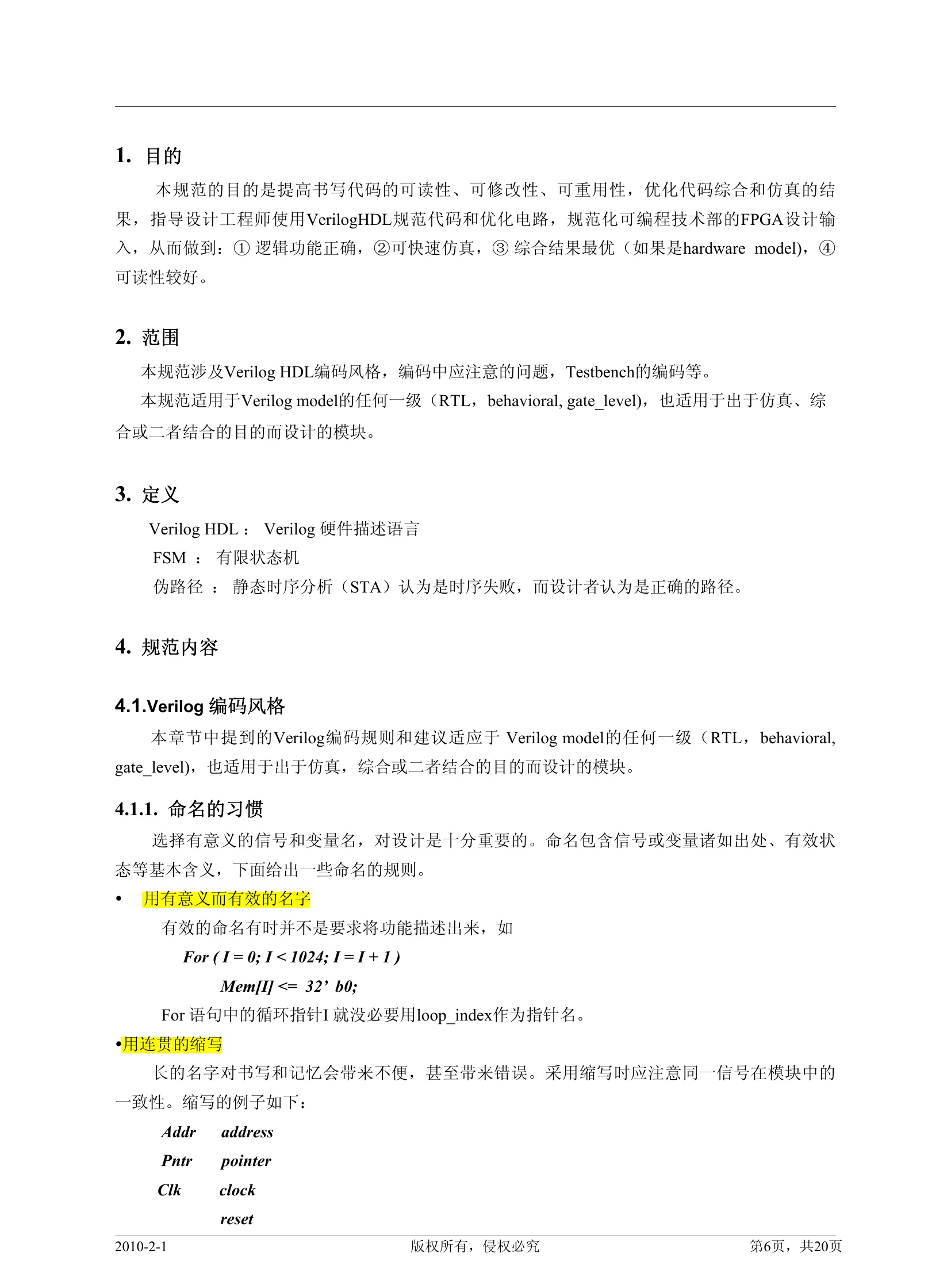

Verilog代码书写规范Release1.目的本规范的目的是提高书写代码的可读性、可修改性、可重用性,优化代码综合和仿真的结果,指导设计工程师使用VerilogHDL规范代码和优化电路,规范化可编程技术部的FPGA设计输入,从而做到:①逻辑功能正确,②可快速仿真,③综合结果最优(如果是hardwaremodel),④可读性较好。2.范围本规范涉及VerilogHDL编码风格,编码中应注意的问题,Testbench的编码等。本规范适用于Verilogmodel的任何一级(RTL,behavioral,gate_level),也适用于出于仿真、综合或二者结合的目的而设计的模块。3.定义VerilogHDL:Verilog硬件描述语言FSM:有限状态机伪路径:静态时序分析(STA)认为是时序失败,而设计者认为是正确的路径。4.规范内容4.1.Verilog编码风格本章节中提到的Verilog编码规则和建议适应于Verilogmodel的任何一级(RTL,behavioral,gate_level),也适用于出于仿真,综合或二者结合的目的而设计的模块。4.1.1.命名的习惯选择有意义的信号和变量名,对设计是十分重要的。命名包含信号或变量诸如出处、有效状态等基本含义,下面给出一些命名的规则。y用有意义而有效的名字有效的命名有时并不是要求将功能描述出来,如For(I=0;I<1024;I=I+1)Mem[I]<=32’b0;For语句中的循环指针I就没必要用loop_index作为指针名。y用

用户评论