并行CRC-32校验码生成算法研究及其实现

在分析串行结构CRC生成算法的基础上,提出了一种高效的8bit并行CRC-32校验码生成算法.利用该算法在特定FPGA芯片上实现了任意字节的CRC-32校验码的生成模块,该模块仅占用93个逻辑单元,最高数据吞吐量可达2400Mbps.

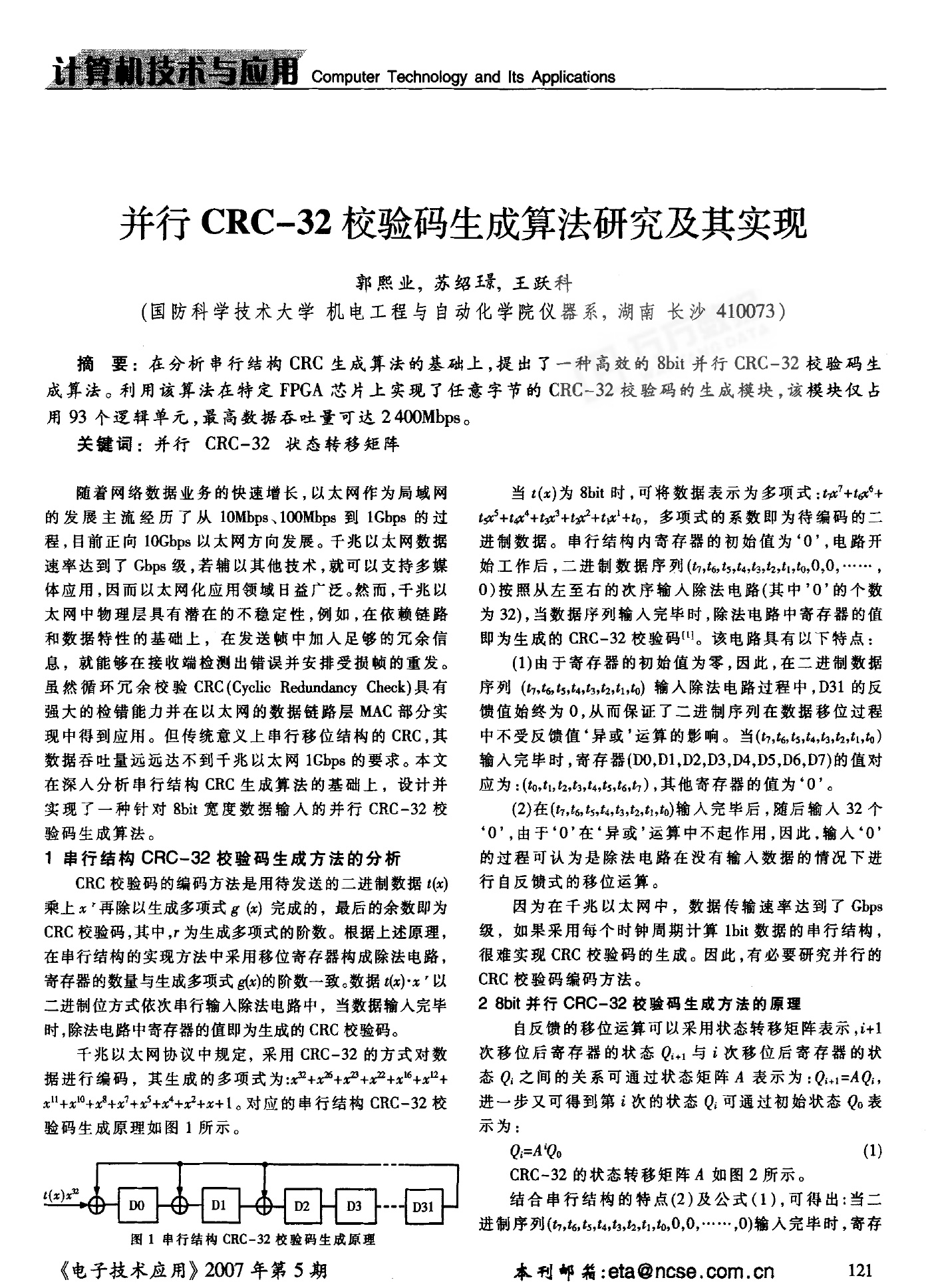

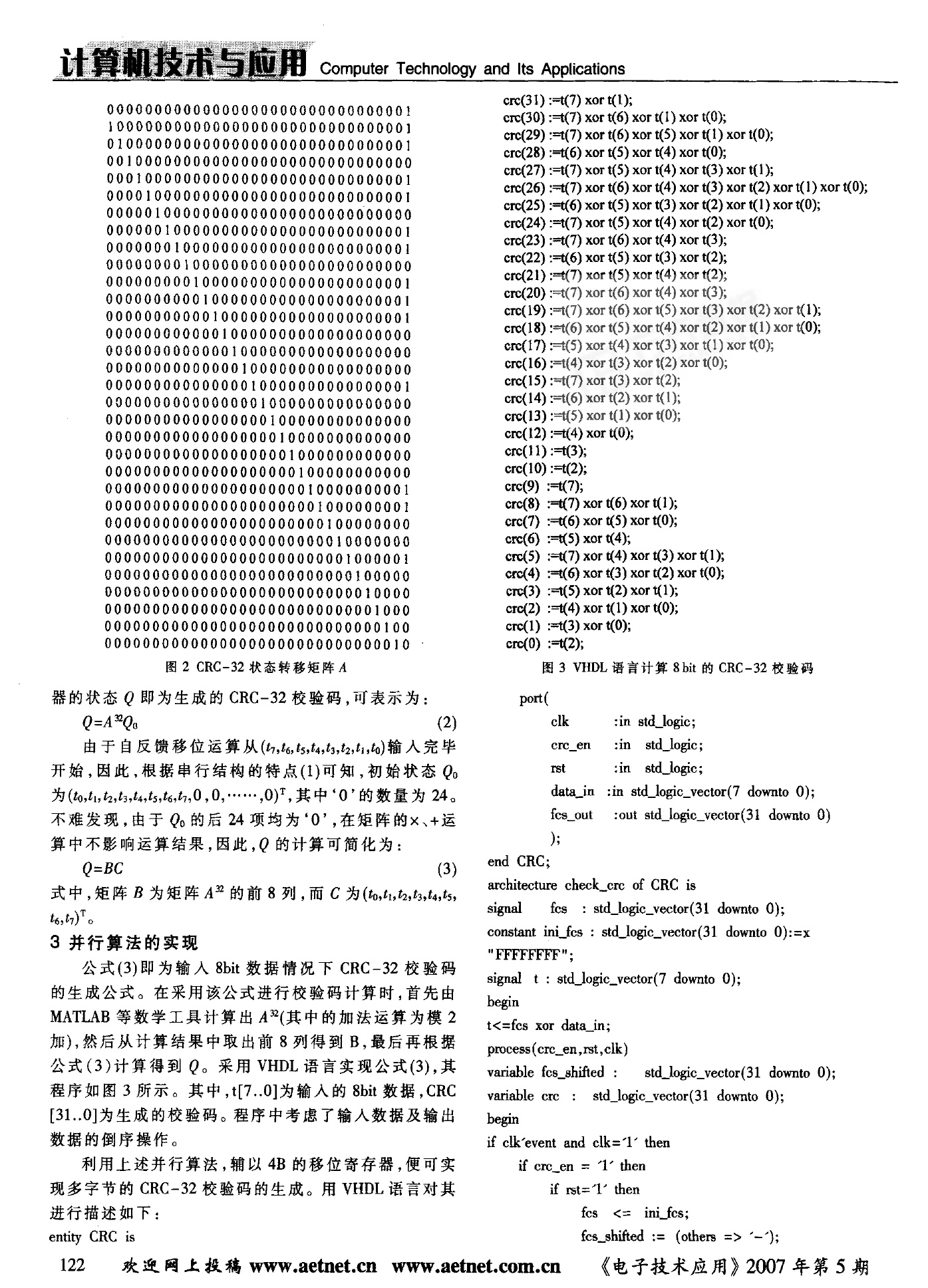

并行CRC一32校验码生成算法研究及其实现郭熙业,苏绍王景,王跃科(国防科学技术大学机电工程与自动化学院仪器系,湖南长沙410073)摘要:在分析串行结构CRC生成算法的基础上,提出了一种高效的8bit并行CRC一32校验码生成算法。利用该算法在特定FPGA芯片上实现了任意字节的CRC~32校验码的生成模块,该模块仅占用93个逻辑单元,最高数据吞吐量可达2400Mbps。关键词:并行CRC一32状态转移矩阵随着网络数据业务的快速增长,以太网作为局域网当t(膏)为8bit时,可将数据表示为多项式:机7+f矿+的发展主流经历了从10Mbps、100Mbps到1Gbp8的过f矿+∥+∥+l矿+t群1+f。,多项式的系数即为待编码的二程,目前正向10Gbps以太网方向发展。千兆以太网数据进制数据。串行结构内寄存器的初始值为‘0’,电路开速率达到了Gbps级,若辅以其他技术,就可以支持多媒始工作后,二进制数据序列(幻,如,岛,“,t3,乞,£I,bO,0,,体应用,因而以太网化应用领域日益广泛。然而,千兆以0)按照从左至右的次序输入除法电路(其中’O’的个数太网中物理层具有潜在的不稳定性,例如,在依赖链路为32),当数据序列输入完毕时,除法电路中寄存器的值和数据特性的基础上,在

用户评论